No Exact Pin Match

Physical Synthesis is more and more popular in logic synthesis. Physical Synthesis tool, Design Compiler Topographical(DCT) or Design Compiler Graphical(DCG) for example, may add hierarchical pins that are not in RTL code and it may cause mapping issue when Implementation Netlist is comparing with Reference Netlist in ECO.

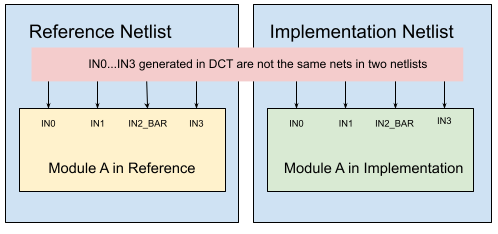

For example, DCT may add 'IN0', 'IN1', 'IN2', 'IN2_BAR' ... to hierarchical modules. The new added pins are not necessarily matching to each other in Implementation Netlist and Reference Netlist. That is, IN0 in module A in Reference Netlist maybe a different signal from IN0 in module A in Implementation Netlist.

Figure 1: No Exact Pin Match

These pins are randomly named in each run. They won't affect logic equivalence check, but they need to be excluded in pin matching in ECO. Otherwise, the ECO tool would insert redundant logic or wrong logic.

API set_noexact_pin_match can be used to resolve the mapping issue between Implementation Netlist and Reference Netlist.

By adding the port naming regular expression in the API argument, set_noexact_pin_match('\bIN\d+(_BAR)?\b'), these ports will be remapped.

Note: This API should be run before reading designs.

# GOF ECO script, run_example_noexact_pin_match.pl

use strict;

undo_eco;

# Discard previous ECO operations

setup_eco(

"eco_example");

# Setup ECO name

read_library(

"art.90nm.lib");

# Read in standard library

set_noexact_pin_match('\bIN\d+(_BAR)?\b'); # The argument is in REGEX format to detect IN0/IN0_BAR/IN1...

# Note: set_noexact_pin_match API should be run before reading designs!

read_svf(

"-ref",

"reference.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_svf(

"-imp",

"implementation.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_design(

"-ref",

"reference.gv");

# Read in Reference Netlist

read_design(

"-imp",

"implementation.gv");

# Read in Implementation Netlist Which is under ECO

set_top(

"SOC_TOP");

# Set the top to the most top module SOC_TOP

set_ignore_output(

"scan_out*");

set_pin_constant(

"scan_enable", 0);

set_pin_constant(

"scan_mode", 0);

fix_design;

save_session(

"current_eco_name");

# Save a session for future restoration

report_eco();

# ECO report

check_design(

"-eco");

# Check if the ECO causes any issue, like floating

write_verilog(

"eco_verilog.v");

# Write out ECO result in Verilog

exit;

# Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

Check No Exact Pin Match in user manual

Follow us:

© 2026 NanDigits Design Automation. All rights reserved.