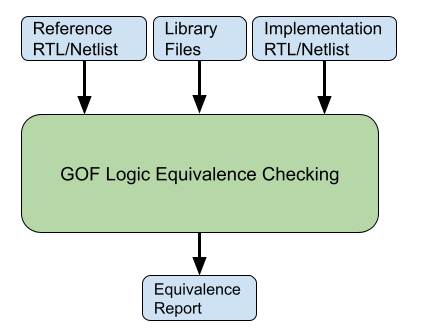

The GOF platform features a built-in powerful logic equivalence checker tool called GOF LEC. While not mandatory, the tool can benefit from SVF files in certain cases. It is strongly advised to utilize SVF files if they are obtainable, especially for designs with multibit flop. The two designs being compared can either be in RTL or Netlist format, with RTL supporting SystemVerilog2017. The read design method differs depending on whether RTL or Netlist is being supported.

Figure 1: GOF LEC Engine

The following is the example script for Netlist to Netlist LEC:

# LEC script, run_net2net_lec.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_svf('-ref', 'AI2023_top_syn.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_svf('-imp', 'AI2023_top_pr.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_design('-ref', 'AI2023_top_syn.v'); # Read in the Reference Netlist, prelayout netlist read_design('-imp', 'AI2023_top_pr.v'); # Read in the Implementation Netlist, postlayout netlist set_top("AI2021_top"); # Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); my $non_equal = run_lec; # Run logic equivalence check on the two netlists if($non_equal){ gprint("LEC failed with $non_equal non-equivalent points"); }else{ gprint("LEC passed"); }

The following is the example script for RTL to Netlist LEC:

# LEC script, run_rtl2net_lec.pl use strict; read_library("art.5nm.lib"); # Read in standard library set_inc_dirs("-ref", "inc_dir_path/include"); set_define("-ref", "NO_SIMULATION", 1); my @rtl_files = ("cpu_core.sv", "mem_ctrl.sv", "display_sys.sv", "chip_top.sv"); read_rtl("-ref", @rtl_files); # Read in the Reference RTL files read_svf('-imp', 'chip_top.svf.txt'); # Optional, must be loaded before read_design, must be in text format read_design('-imp', 'chip_top.v'); # Read in the Synthesis Netlist set_top("CHIP_TOP"); # Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); elab_rtl(); # RTL processing my $non_equal = run_lec; # Run logic equivalence checking on RTL vs Netlist if($non_equal){ gprint("LEC failed with $non_equal non-equivalent points"); }else{ gprint("LEC passed"); }