An ECO is considered unfriendly to DFT if it impairs DFT functionality or diminishes DFT coverage. On the other hand, a DFT friendly ECO must ensure that DFT functionality remains unaffected, scan chain is intact, and clock and reset signals are manageable.

During functional ECO, the DFT logic should be set to inactive mode to prevent any functional changes from affecting it. However, in some cases, ECOs involving DFT paths may unintentionally impact the DFT logic.

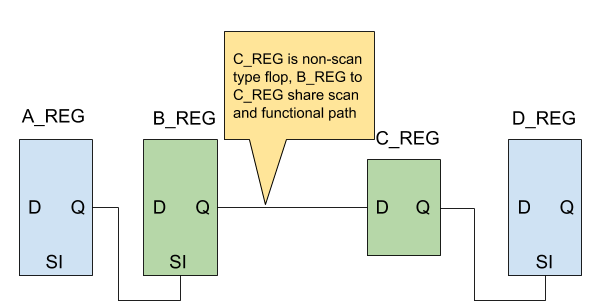

One example of this is when ECO insertion is performed on back-to-back flops in a partial scan chain, such as the one shown from A_REG to D_REG, with B_REG and C_REG forming a back-to-back path. In this scenario, it's acceptable for C_REG to be a non-scan flop prior ECO and DFT is good.

Figure 1: Scan Chain with back-to-back flops

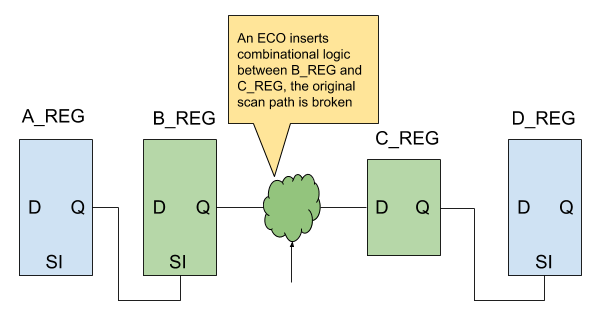

If an ECO inserts combinational logic between B_REG and C_REG in a scan chain that goes from A_REG to D_REG, and C_REG is a non-scan flop, then the scan chain is broken, as shown in Figure 2. Conformal ECO breaks DFT by directly inserting logic in the back-to-back path in this type of ECO, without considering the need to keep the scan chain.

Figure 2: ECO inserts logic into back-to-back path

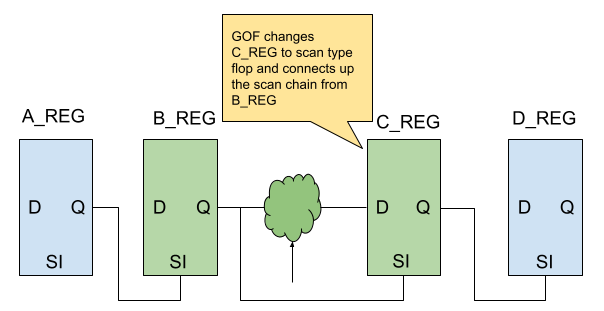

To address the scan chain breakage caused by the ECO, GOF's solution involves changing the type of C_REG from a non-scan flop to a scan flop, and connecting the scan chain properly as depicted in Figure 3.

Figure 3: GOF fixes the DFT logic by reconnecting up the Scan Chain

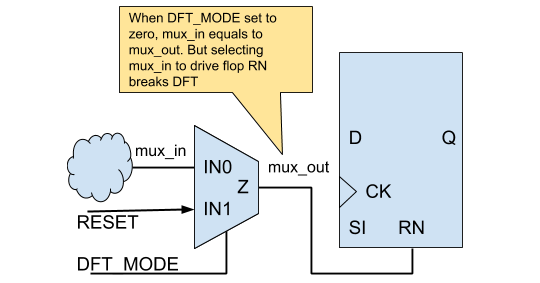

To ensure DFT logic remains inactive during functional ECO, the DFT_MODE signal is set to zero. However, some nets may be equivalent but not suitable for DFT, which can lead to DFT being broken. For instance, in Figure 4, an ECO must select either the mux_in or mux_out signal to drive a reset pin of a flop. Although the two signals are equivalent, Conformal ECO selects mux_in, which breaks DFT. In contrast, GOF can identify the MUX and chooses mux_out as the correct signal for the reset pin, thus maintaining the integrity of DFT logic.

Figure 4: Pick the right signal to maintain DFT logic

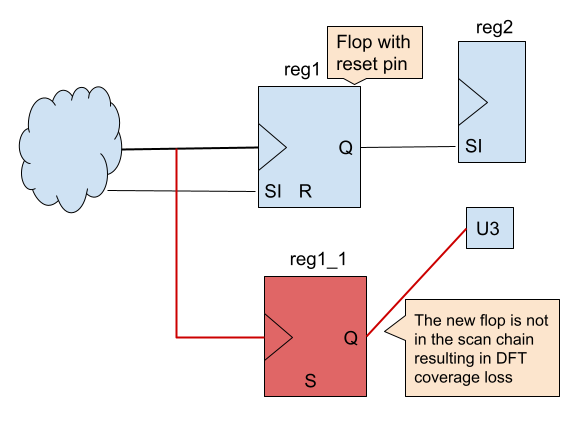

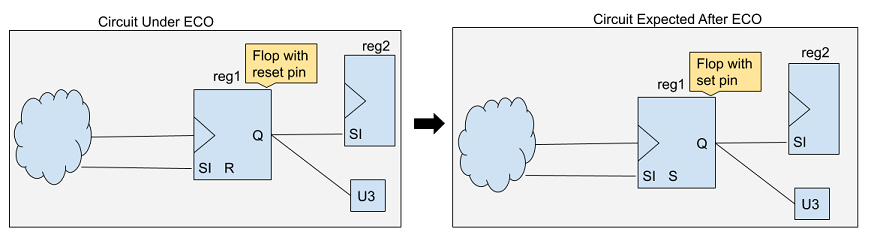

When performing functional netlist ECO, it is common to swap between resettable and settable flop types. This operation is assumed to be a simple and straightforward swapping of the same flop instance. However, in figure 5, Cadence Conformal introduces a redundant approach by using a new settable type flop reg1_1 instead of directly converting the original flop to a settable type. The new flip-flop reg1_1 drives the original functional circuit, while the old flip-flop reg1 drives the scan chain fanout reg2. This approach presents two major issues. Firstly, the new flip-flop reg1_1 is not included in the scan chain. In situations where there are many such reset/set flop swaps (around 0.2% of all flop count), there will be an approximately 0.2% loss in ATPG at-speed coverage. Secondly, Conformal LEC fails to consider the new flip-flop reg1_1 as an equal key point of reg1, resulting in numerous non-equivalent points in the equivalence report after the ECO.

Figure 5: Cadence Conformal causes DFT coverage loss in resettable/settable flop swapping ECO

While, in the ECO shown in Figure 6, GOF utilizes a direct approach of changing the flip-flop type from resettable to settable, resulting in the preservation of the scan chain and ensuring that DFT coverage remains unaffected.

Figure 6: Resettable flop swapped to settable type in ECO

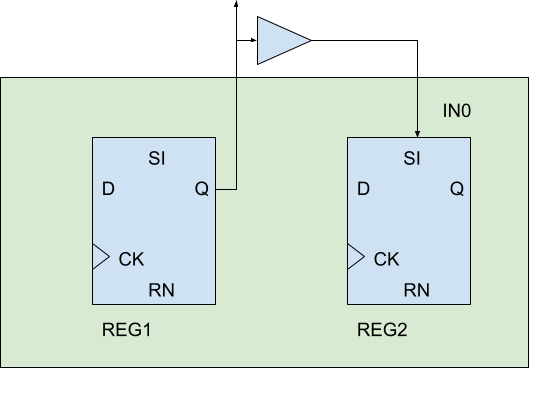

One error is common in Cadence Conformal ECO, "Error: Duplicate fanout branch # for net 'IN#'"

The issue typically arises in a scenario where a flip-flop (REG1) has its Q output connected to the parent level, and the same output is also connected to the scan input (SI) pin of another flip-flop (REG2). When an ECO is performed on REG1, such as changing its type to a set-type flip-flop, this can cause an error to occur in Conformal ECO, potentially leading to the tool stopping its operation.

Figure 7: Cadence Conformal errors out in boundary wire changes

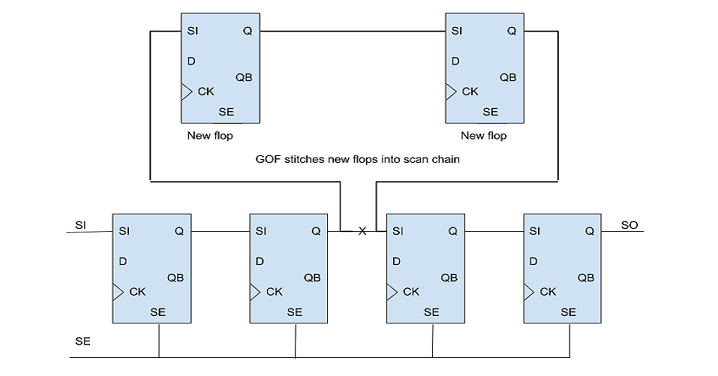

To prevent any loss of DFT coverage, it is recommended to integrate new flops added in an ECO into the existing scan chains. Industrial data suggests that in a design with 100K flops, 100 newly added non-scan flops can lead to a DFT coverage loss of over 0.1%. Such loss of DFT coverage is unacceptable for high-reliability chips, such as those used in automobiles. Therefore, if there are any new flops introduced in a functional ECO, it is necessary to redo the scan chain to incorporate the new flops.

Figure 8: Stitch scan chain

There are multiple methods available in GOF to insert new flops into scan chains. One option is to utilize the 'stitch_scan_chain' API, which automatically integrates the new flops into the scan chains. Alternatively, there are several netlist processing APIs that can be used to manually insert the new flops into the scan chains.

Automatic mode to insert flops into a scan chain in the local modules

An automatic method can be used to integrate flops into a scan chain within local modules. In the following example script, suppose the 'fix_design' command adds eight new flops named 'state_new_reg_0' to 'state_new_reg_7'. To integrate these flops into the scan chain within the local module:

Automatic mode to insert flops before one flop

GOF offers an automatic method to insert new flops before a specified flop instance. Users can identify the instance name of one flop, and GOF will insert all new flops into the scan chain before that instance.

For instance, let's say it is required to integrate all the new flops into the scan chain prior to the instance named 'u_pixel_ctrl/pulse_reg':

Manual mode to connect up all new flops

The scan chain can be re-connected up manually by ECO APIs. And new scan in/out ports are created.

# GOF ECO script, run_manual_stitch_scan_chain_example.pl use strict; undo_eco; # Discard previous ECO operations setup_eco("eco_manual_stitch_scan_chain_example");# Setup ECO name read_library("art.5nm.lib");# Read in standard library read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design; save_session("current_eco_name"); # Save a session for future restoration set_error_out(0); # Don't exit if finds error my @flops = get_cells("-hier", "-nonscan"); # Find all new flops that are not in scan chain yet # @flops can be defined by reading a list file if(scalar(@flops)){ # If there are new flops, start the work new_port("so1", "-output"); # New a scan out port so1 new_port("si1", "-input"); # New a scan in port si1 my $cnt = 0; my $now_si; foreach my $flop (@flops){ $cnt++; if(is_scan_flop($flop)==0){ my $flop_name = get_ref($flop); my $scanflop = get_scan_flop($flop_name); # If the flop is not scan type, change to scan type flop change_gate($flop, $scanflop); } if($cnt==1){ change_port("so1", "$flop/Q"); # The first flop drives the new scan out port }else{ change_pin($now_si, "$flop/Q"); } $now_si = "$flop/SI"; change_pin("$flop/SE", "te"); # All scan enable pin is connected to scan enable signal } change_pin($now_si, "si1"); # The last flop has the new scan in port driving SI pin } write_verilog("eco_verilog.v");# Write out ECO result in Verilog exit;

In conclusion, the DFT friendly ECO is a highly desirable solution for netlist modification processes, as it provides several benefits over traditional methods. One of the most significant advantages is the ability to ensure that the generated designs are DFT friendly, which simplifies the testing and verification process. This is especially important in the modern era of complex integrated circuits, where ensuring DFT compatibility is critical for efficient and reliable testing.

One of the key features of the DFT friendly ECO is its ability to keep the design for testability without compromising on functionality or performance. This is achieved through advanced algorithms and methodologies that take into account the specific DFT requirements of the design. In contrast, traditional EDA processes may not be optimized for DFT, leading to significant challenges in testing and verification.

Furthermore, the use of DFT friendly ECO can provide a competitive advantage in the marketplace. This is because it enables faster time-to-market, reduces design iterations, and improves overall product quality. In comparison, competitors who are not using DFT friendly methodologies may struggle to achieve similar results, leading to delays, increased costs, and reduced product competitiveness.

Overall, GOF's DFT friendly ECO is a highly effective solution for netlist ECO processes, providing significant benefits over traditional methods. Its ability to optimize designs for DFT compatibility can lead to faster time-to-market, reduced design iterations, and improved product quality, providing a competitive advantage in the marketplace.