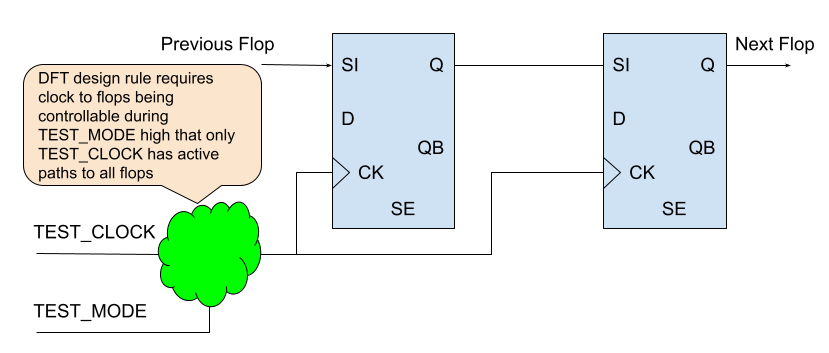

It's common for DFT logic to be broken during functional ECO processes, which involve modifying a design for functional reasons after it has already been verified. Since DFT control signals are disabled during functional ECO, the ECO tool is not aware that DFT logic has been modified and cannot verify its functionality. When the modified netlist is ready to be tested using DFT tool, it can take a long time to identify issues. GOF provides a fast DFT Design Rule Checker that can quickly identify issues with DFT logic. A fundamental design rule for DFT is to ensure that the scan chain is complete, meaning that it can be used to capture and output test patterns during testing. Additionally, clock and reset signals should be controllable during test mode to enable proper test pattern application.

Figure 1: DFT Design Rule Checker

The script to do DFT Design Rule Check:

set_log_file("dft_drc.log"); # Set log file name read_library("art.5nm.lib"); # Read in liberty file read_design('-imp', 'dft_top.v'); # Read in the design with DFT implemented set_top("DFT_TOP"); # Set the top module name set_pin_constant("test_scan_shift", 1); # Set scan shift pin to 1 set_pin_constant("all_test_reg/Q", 1); # Set TDR all_test register Q to 1 set_pin_constant("test_mode_reg/Q", 1); # Set TDR test_mode register Q to 1 create_clock("occ_add_1_inst/U0/Z", 10); # Set clock on OCC drivers, maybe multiple create_clock("occ_add_2_inst/U0/Z", 10); # Set clock on OCC drivers, maybe multiple create_reset("power_on_reset", 0); # Set reset pin set_top("DESIGN_TOP"); # pin_si/pin_so is internal pins of DFT_TOP set_scan_pairs("pin_si[0]", "pin_so[0]"); # Add scan chain pair 0 set_scan_pairs("pin_si[1]", "pin_so[1]"); # Add scan chain pair 1 # More scan chain can be added. These codes can be handled by a for loop command set_top("DFT_TOP"); my $err = dft_drc; if($err){ gprint("DFT DRC found $err errors\n"); }

The Design Rule Checker can catch these issues by error codes:

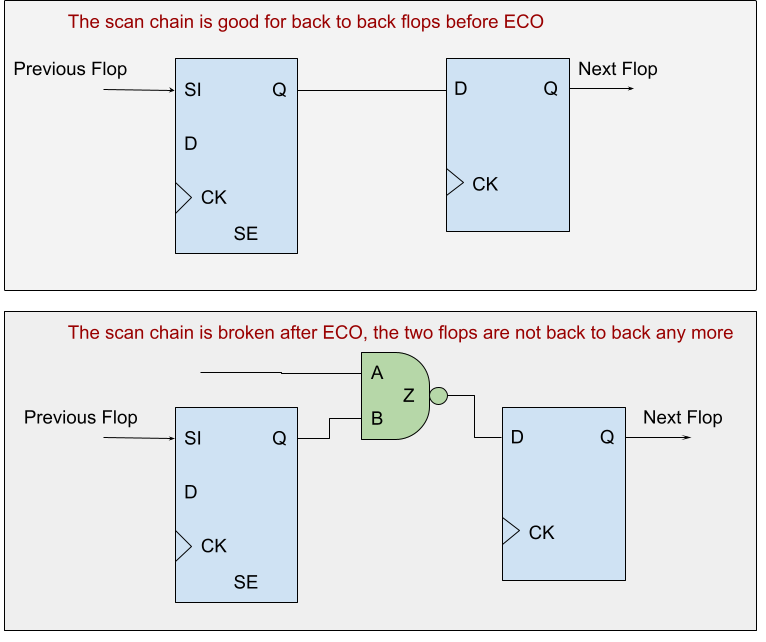

For instance, DFT DRC catches ERROR_MULTI_PATHS error in a functional ECO when an NAND gate is inserted between back-to-back flops.

Figure 2: Broken scan chain in functional ECO

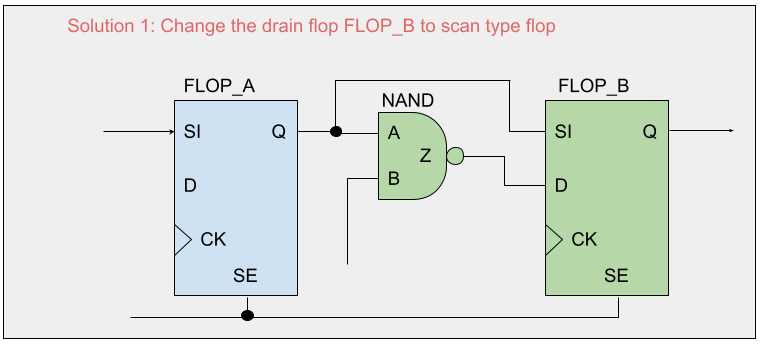

There are two solutions to fix the error. The first solution involves changing the drain flop, FLOP_B, to a scan type flop with scan_in and scan_enable pins.

Figure 3: Solution 1 to change the drain flop scan type

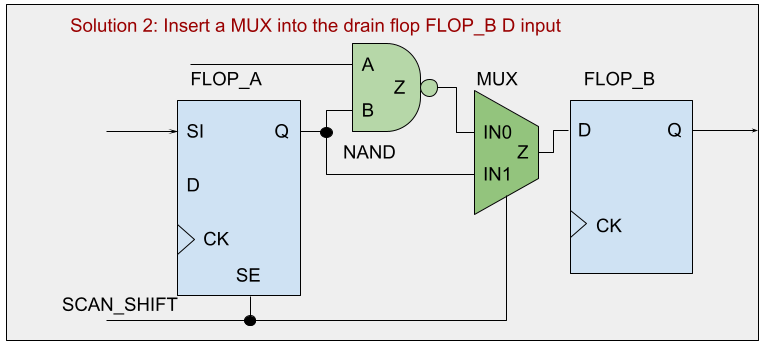

The second solution involves inserting a MUX before the D input of FLOP_B. The selection signal of the MUX is controlled by the scan_enable signal to select the output of the previous flop, FLOP_A, when scan_enable is asserted.

Figure 4: Solution 2 to insert a MUX to fix the scan chain

Both solutions can be implemented using GOF in either GUI mode ECO or script mode ECO. After the necessary fixes have been made, the DFT DRC will be free of errors.

For more information on GUI mode ECO, please refer to this page.

The commands to fix the logic in script mode:

#Solution 1 change_gate("FLOP_B", "SDFFHQX1", ".SI(FLOP_A/Q),.SE(FLOP_A/SE)"); #Solution 2 change_pin("FLOP_B/D", "MX2X4", "u_dft_eco_mux", "-,FLOP_A/Q,FLOP_A/SE");

Check DFT Design Rule Checker in user manual