DFT Constraints for LEC and ECO

To prevent false non-equivalence in LEC and ECO, constraints must be placed on the DFT logic. In the traditional DFT flow, the DFT logic is typically incorporated into the RTL design, which appears in both the Reference Netlist and the Implementation Netlist. In contrast, the modern DFT flow, which supports IEEE1687 and IEEE1500 standards, inserts the DFT logic into the Implementation Netlist using a DFT tool like Mentor Tessent. To ensure that the Implementation Netlist, which contains DFT logic inserted by the DFT tool, matches the Reference Netlist, which lacks DFT logic, a Logic Equivalence Check must be performed. To prevent redundant or false ECO fixes, the DFT logic must be correctly constrained in the automatic functional ECO process.

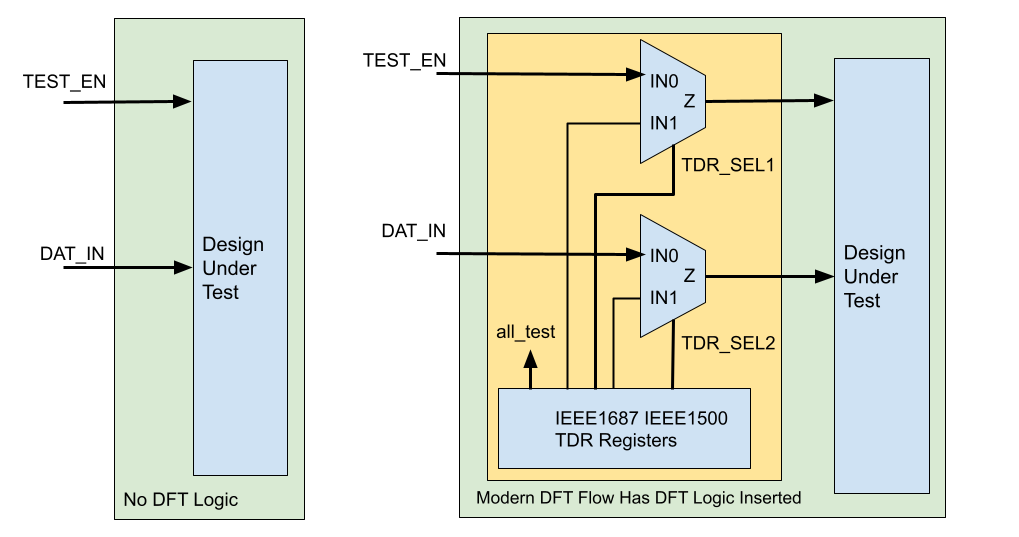

In the traditional DFT flow, as illustrated in the left side of Figure 1, constraints are placed on the ports. For instance, DFT control signals such as TEST_EN are set to zero, while the normal functional ports are left unconstrained.

Figure 1: DFT Constraints in Automatic Functional ECO

In the modern DFT flow, these inserted DFT logic by the DFT tool as shown in the right side of Figure 1 should be constrained to be in inactive state. The control signals driven by TDR registers should be constrained to zeros.

GOF provides several APIs to constrain the DFT logic, set_ignore_output, set_pin_constant and set_net_constant. The API set_net_constant can be used to constrain the TDR registers signals. Since TDR registers are not ports, so they have be treated as nets.

The full script with constraints on the traditional DFT flow is shown below:

# GOF ECO script, run_example_exclude_test_logic.pl

# The SOC_TOP design should have scan insertion test logic excluded in ECO.

# The scan out bus pin has naming of scan_out[199:0] and API set_ignore_output can be used to exclude LEC check on scan_out in ECO.

# And TEST_EN and scan_mode are two scan set up signals which can be forced to zeros by API set_pin_constant.

use strict;

undo_eco;

# Discard previous ECO operations

setup_eco(

"eco_example");

# Setup ECO name

read_library(

"tsmc.lib");

# Read in standard library

read_svf(

"-ref",

"reference.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_svf(

"-imp",

"implementation.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_design(

"-ref",

"reference.gv");

# Read in Reference Netlist

read_design(

"-imp",

"implementation.gv");

# Read in Implementation Netlist Which is under ECO

set_top(

"SOC_TOP");

# Set the top to the most top module SOC_TOP

set_ignore_output(

"scan_out*");

set_pin_constant(

"TEST_EN", 0);

set_pin_constant(

"scan_mode", 0);

fix_design;

save_session(

"current_eco_name");

# Save a session for future restoration

report_eco();

# ECO report

check_design(

"-eco");

# Check if the ECO causes any issue, like floating

write_verilog(

"eco_verilog.v");

# Write out ECO result in Verilog

exit;

# Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The full script with constraints on the modern DFT flow is shown below:

# GOF ECO script, dft_constraints_on_inserted_test_logic.pl

# set_net_constant is used to constrain TDR register nets to zeros

use strict;

undo_eco;

# Discard previous ECO operations

setup_eco(

"eco_example");

# Setup ECO name

read_library(

"tsmc.lib");

# Read in standard library

read_svf(

"-ref",

"reference.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_svf(

"-imp",

"implementation.svf.txt");

# Optional, must be loaded before read_design, must be in text format

read_design(

"-ref",

"reference.gv");

# Read in Reference Netlist

read_design(

"-imp",

"implementation.gv");

# Read in Implementation Netlist Which is under ECO

set_top(

"SOC_TOP");

# Set the top to the most top module SOC_TOP

set_ignore_output(

"scan_out*");

set_pin_constant(

"TEST_EN", 0);

set_pin_constant(

"scan_mode", 0);

set_net_constant("TDR_SEL0", 0, "-imp"); # TDR register net only exists in Implementation Netlist

set_net_constant(

"TDR_SEL1", 0,

"-imp");

set_net_constant(

"all_test", 0,

"-imp");

fix_design;

save_session(

"current_eco_name");

# Save a session for future restoration

report_eco();

# ECO report

check_design(

"-eco");

# Check if the ECO causes any issue, like floating

write_verilog(

"eco_verilog.v");

# Write out ECO result in Verilog

exit;

# Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

Check DFT Constraints on User Manual for detail

Follow us:

© 2026 NanDigits Design Automation. All rights reserved.