The DFT logic is disabled in functional netlist ECO by setting constraints, but in order to fix DFT logic in the automatic netlist ECO, these constraints must be removed. The Reference Netlist's DFT logic serves as a guide for repairing the Implementation Netlist. However, the DFT automatic ECO process only addresses DFT logic with fixed naming conventions. In complex DFT designs, DFT tools may add flops with random naming styles, such as the IEEE1500 wrapper cell feature. For such designs, users may need to rely on manual ECOs to make changes to the DFT logic.

The DFT scripts have been revised to include new features, such as the addition of a TDR register. The DFT tool is utilized to incorporate the new DFT logic into the design, and the resulting netlist, including the DFT logic, is saved as the Reference Netlist.

The GOF ECO script reads the Reference Netlist to repair the Implementation Netlist.

Here is the detailed script for DFT automatic ECO:

# GOF ECO script, run_dft_auto.pl use strict; setup_eco("eco_dft_auto");# Setup ECO name read_library("art.5nm.lib");# Read in standard library read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "dft_new_ref.gv");# Read in Reference Netlist with new DFT read_design("-imp", "postnetlist_old_dft.gv");# Read in Implementation Netlist Which is under ECO set_top("top_wrapper");# Set the top module fix_design(); report_eco(); # ECO report write_verilog("imp_dft_eco.gv");# Write out ECO result in Verilog gexit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

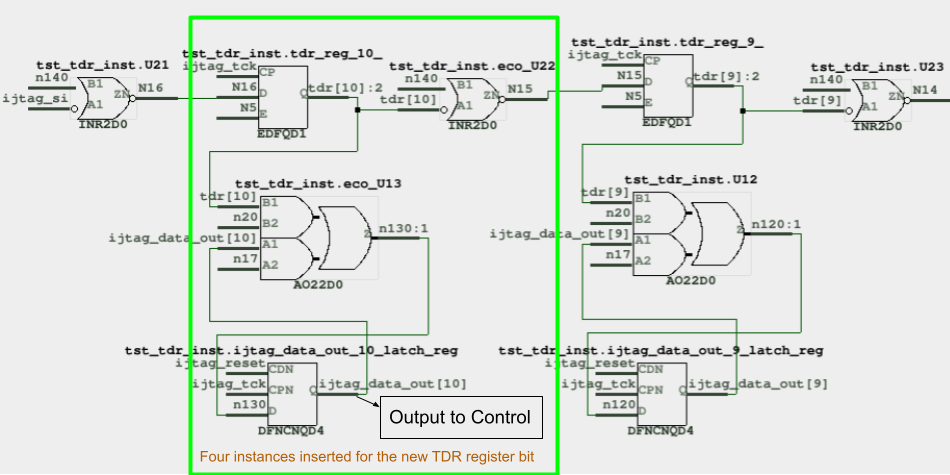

The following figure shows the DFT logic having one TDR register added. Four new instances are added in the ECO

Figure 1: Automatic DFT ECO