The use case shows how to automatically fix the selected modules in implementation netlist. Only when RTL changes are known to be isolated inside the specified modules.

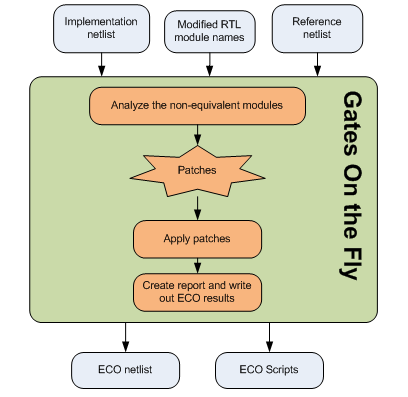

Users provide Implementation netlist which is under ECO, Reference netlist which is re-synthesized after RTL modification and the name of top level module that contains the changes.

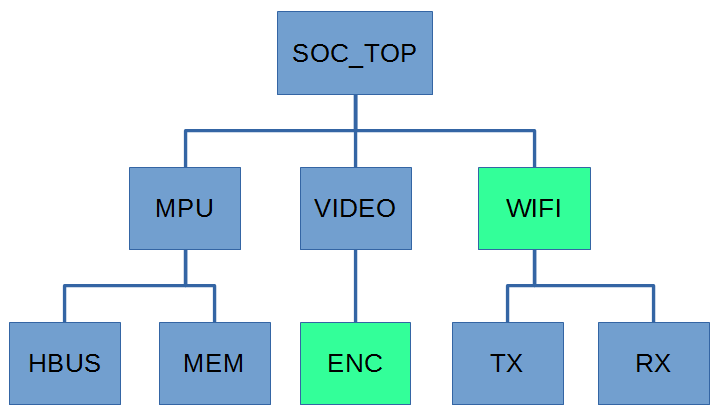

A hierarchical design as shown in the chart below is known to have only two modules modified, WIFI and ENC, and the changes are isolated in these two modules not propagating through hierarchical ports.

ECO API, 'fix_module' can be run on these two modules

# GofCall ECO script, auto_eco.pl use strict; undo_eco; # Discard previous ECO operations setup_eco("eco_example"); # Setup ECO name read_library("art.90nm.lib"); # Read in standard library # Read in the Reference Netlist which is re-synthesized with several modules modified read_design("-ref", "reference.gv"); # Read in the implementation Netlist Which is under ECO read_design("-imp", "implementation.gv"); # Fix these two modules, ENC and WIFI fix_modules('WIFI', 'ENC'); set_top('SOC_TOP'); report_eco(); # ECO report write_verilog("eco_verilog.v"); # Write out ECO result in Verilog write_soce("eco_soce.tcl"); # Write out TCL script for SOC Encounter exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The above script can be run by '-run' option in GOF command line: