When ECO involves clock tree, the clock buffer cells would be removed or re-connected randomly in automatic ECO. GOF provides a feature to preserve the clock tree buffers when fixing clock tree. This use case demonstrates how to fix a clock tree by GOF.

After Placement and Route, clock buffer tree has been built on clock path. Any big change to the buffer tree will bring difficulty to the final timing closure. Any ECO involving clock tree should do a minimum change to the buffer tree.

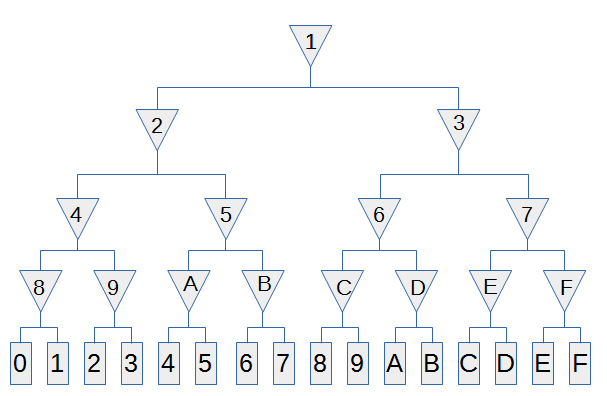

In Figure 1, clock buffer tree cells are illustrated in triangles and flip-flop groups are illustrated in rectangles. The clock skews to all 16 flip-flop groups have been balanced.

Figure 1: Clock Tree in the implementation netlist

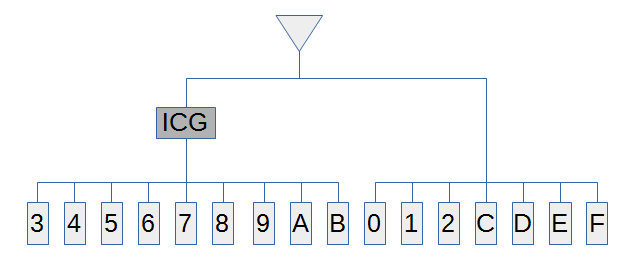

An ECO is to be implemented on the clock tree to insert Integrated Clock Gating (ICG) cell to 9 groups of the flip-flop clusters. As shown in Figure 2, flip-flop groups, 3,4,5,6,7,8,9,A and B will have an ICG inserted to the clock path. GOF provides a feature to insert ICG cells to the implementation netlist with minimum impact.

Figure 2: ICG inserted in the reference netlist

GOF takes the implementation netlist with clock tree in Figure 1 and the reference netlist with ICG inserted in Figure 2.

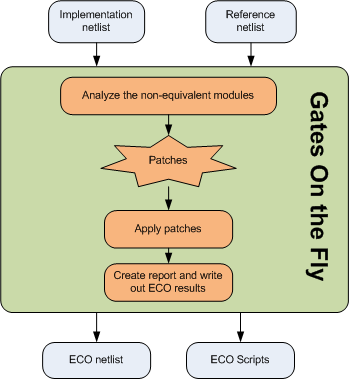

As shown in Figure 3 flow chart, GOF reads in the two netlists and processes the non-equivalent clock paths. The ECO result has the clock tree fixed with three ICG cells inserted.

Figure 3: Auto ECO Flow Chart

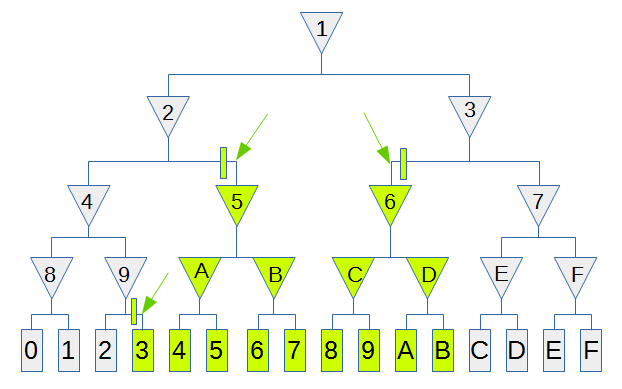

In Figure 4, the final ECO result has only three ICG cells inserted. And it is the optimal result.

Figure 4: Three ICG cells inserted

# GofCall Clock Tree ECO script, clock_tree_eco.pl use strict; undo_eco; # Discard previous ECO operations setup_eco("clk_eco_example"); # Setup ECO name read_library("art.90nm.lib"); # Read in standard library # Read in the Reference Netlist which is re-synthesized with several modules modified read_design("-ref", "reference.gv"); # Read in the implementation Netlist Which is under ECO read_design("-imp", "implementation.gv"); set_top("topmod"); # Set the top module set_ignore_output("TEST_SO*"); # To avoid test lockup to affect the ECO result # Don't set_pin_constant as in Functional Automatic ECO example. It can avoid messing up clock path before and after test MUXs # Fix the Clock Tree in the top module and its sub-modules, -clock option is used in fix_design command fix_design('-clock'); report_eco(); # ECO report write_verilog("eco_verilog.v"); # Write out ECO result in Verilog write_soce("eco_soce.tcl"); # Write out TCL script for SOC Encounter exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The same method can apply to Reset Tree as well. The only change is to replace '-clock' option by '-reset' in fix_design command in the above example code.

The above script can be run by '-run' option in GOF command line: