In modern IC design, the complexity of Design for Test (DFT) flows presents significant challenges. One common issue is the omission of DFT constraints during logic equivalence checking (LEC) and functional netlist ECO. This oversight often results in false non-equivalence reports in LEC and unnecessary modifications in netlist ECO, potentially compromising the integrity of the DFT logic. Given the intricate nature of DFT flows and the diverse tools employed in LEC and netlist ECO, such as Formality for LEC and GOF ECO for netlist modifications, it is challenging to ensure DFT constraints are correctly applied in the initial stages. GOF Debug offers a counter example back-annotation feature that can effectively identify missing DFT constraints, simplifying the debugging process.

Missing DFT constraints can lead to:

GOF Debug provides a powerful feature to address these issues: counter example back-annotation. This method involves:

Running an Initial LEC: Perform an LEC using GOF Debug to identify all non-equivalent points between the implementation and reference netlists.

Loading Instances into the Schematic: Select one non-equivalent flop and load both the implementation and reference instances into the same schematic.

GOF > sch tsp_reg -both

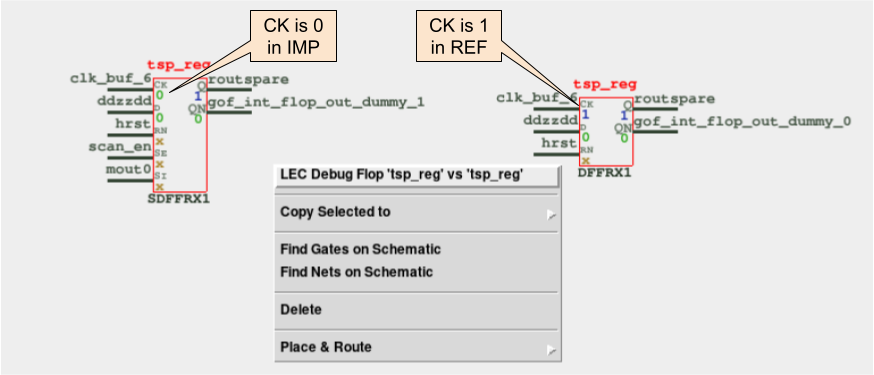

LEC Debug Run on the Schematic: Execute a debug run on the loaded schematic. The tool will back-annotate non-equivalence information directly onto the schematic. As shown in Figure 1, the CK pins have different values annotated.

Figure 1: LEC Debug on two flops

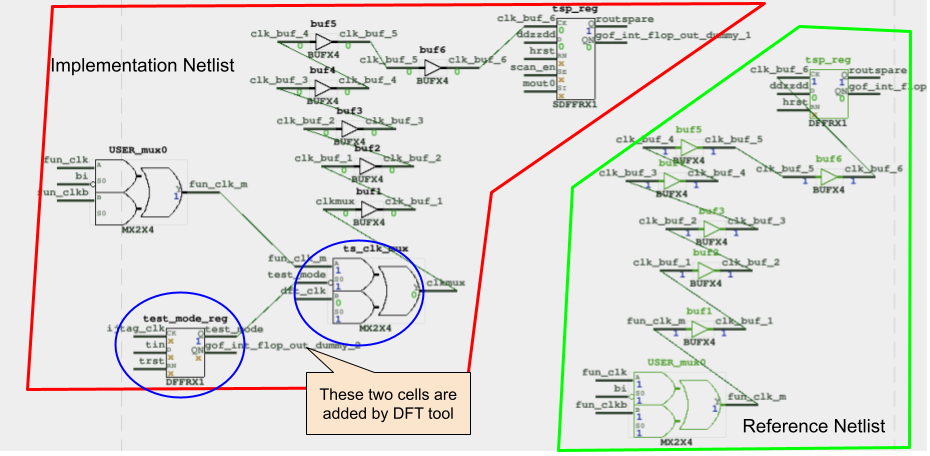

Isolating the Missing DFT Constraint: From Figure 1, the CK pin has different annotated values in the Implementation and the Reference netlist. Expand the schematic starting from the CK pins. By expanding, the schematic quickly reveals the root cause: the DFT tool inserted instances without a constant constraint on the test_mode signal. This makes it straightforward to isolate the exact point where the DFT constraint is missing.

Figure 2: Pinpoint the missing DFT constraint by counter example back-annotation

The counter example back-annotation feature in GOF Debug is an invaluable tool for quickly and accurately pinpointing missing DFT constraints in complex IC designs. By leveraging this feature, designers can streamline the debugging process, ensure the integrity of DFT logic, and improve overall design efficiency. As DFT flows continue to evolve, tools like GOF Debug will play a crucial role in maintaining the accuracy and reliability of IC designs.