GOF ECO outperforms Conformal ECO by excelling in various performance aspects. Conformal ECO frequently encounters critical errors during functional ECO, such as:

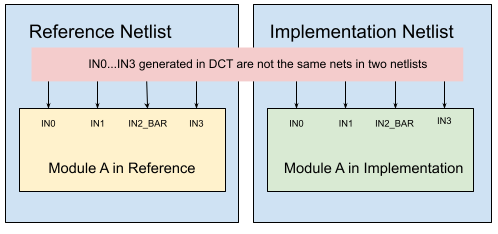

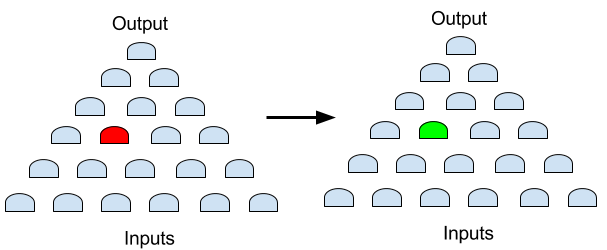

Conformal ECO appears to grapple with algorithmic challenges when dealing with certain corner cases in netlists. In the case of gate-level netlists with millions of gates, the multitude of combinations introduces numerous corner cases. While the specific reasons for Conformal ECO failures remain elusive, several potential causes are plausible. Notably, Conformal ECO struggles to adeptly manage boundary-optimized designs. Illustrated in the figure below, both the synthesis tool and the back-end tool have a tendency to introduce additional ports that were not present in the original design, posing a challenge for Conformal ECO.

Figure 1: Conformal ECO has issue in handling boundary optimization

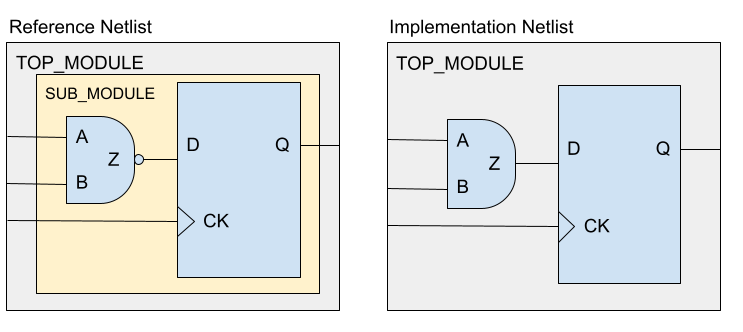

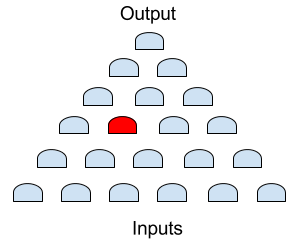

Another contributing factor could be the presence of unmapped hierarchies. Conformal ECO may encounter difficulties in addressing mapped key points within these unmapped hierarchies, as illustrated below.

Figure 2: Conformal ECO has issue in handling unmapped hierarchies

These errors pose substantial challenges in Conformal ECO, lacking viable solutions or alternatives. When users encounter these issues, Conformal ECO falls short in producing an effective patch, compelling them to resort to abandoning the ECO process and initiating a restart with a newly generated netlist for the back-end. This setback significantly impacts the project schedule.

Moreover, even if Conformal ECO manages to generate a patch without the aforementioned errors, the resulting ECO netlist frequently faces difficulties in passing logic equivalence checking. This is especially pronounced when the patch involves hundreds or thousands of gates.

In contrast, GOF ECO effectively tackles and overcomes these challenges where Conformal ECO falls behind. GOF ECO integrates a powerful algorithm for restoring nets in boundary-optimized designs. Moreover, it exhibits accuracy in managing ECO tasks that encompass mapped flops across distinct hierarchies. Notably, GOF ECO boasts a significantly higher success rate, particularly when dealing with ECO patches involving hundreds or thousands of gates.

When evaluating ECO quality under the condition of Conformal ECO results passing logic equivalence checking, there are several identified performance issues. Firstly, Conformal ECO exhibits suboptimal performance on netlists generated by Synopsys Design Compiler Topographical (DCT) or Design Compiler Graphical (DCG). Secondly, it encounters a bug in effectively handling complex combinational logic during ECO. Thirdly, it demonstrates inadequacy in addressing ECOs involving DFT scan chains.

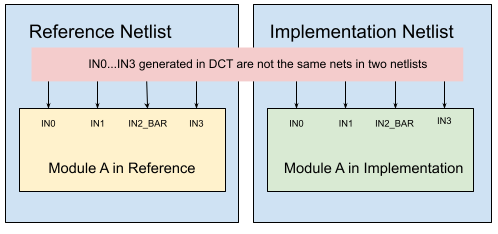

Synopsys Design Compiler Topographical (DCT) and Design Compiler Graphical (DCG) are tools that optimize netlists for floorplanning, routing, and timing. However, they can make functional ECO more difficult. During synthesis, they can change hierarchical module boundaries to add clone ports or invert the original ports' phase and merge flops.

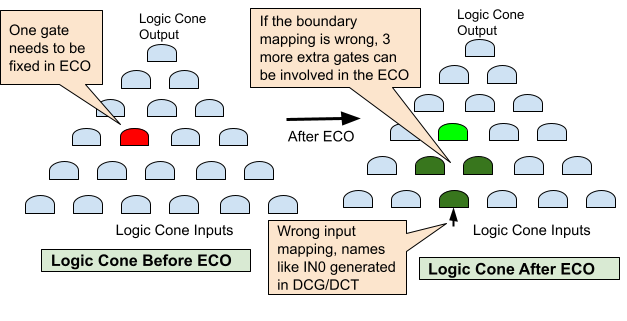

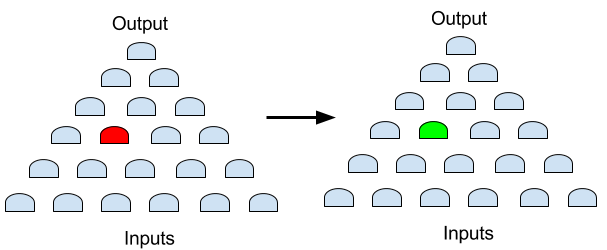

Conformal ECO has issues with ports mapping in functional ECO. As shown in Figure 3, Conformal ECO incorrectly maps the clone ports added by DCG/DCT, resulting in three times more gates being used than necessary to fix the logic.

Figure 3: Boundary mapping affects ECO quality

The synthesis tool adds cloned ports that do not have a one-to-one mapping between the Reference Netlist and the Implementation Netlist. When the ECO tool attempts to make these ports equal, it can result in redundant gates being added to the ECO patch or even make the final logic not equivalent.

Figure 4: DCG/DCT Boundary optimized netlist

However, GOF is able to map the clone ports correctly, ensuring that only the exact non-equivalent point is fixed.

Figure 5: GOF result, only the red spot is fixed

In the world of RTL (Register Transfer Level) design, combinational signals are frequently optimized after synthesis, making it a daunting task to manually locate the precise ECO (Engineering Change Order) points. To tackle this challenge, advanced Logic ECO tools are utilized. These tools leverage comprehensive algorithms to accurately identify and measure the size of the ECO patch, a crucial factor in the success of ECO, especially in post-mask metal only ECO scenarios where resources are scarce and timing closure becomes exceedingly difficult with the involvement of too many spare cells.

However, Conformal ECO has a bug in handling complicated combinational logic ECO.

Conformal ECO's limitations are evident in two key areas:

To illustrate, consider a scenario (depicted in Figure 6) involving a single combinational signal within a large combination logic cone that has been modified. The task for the ECO tool here is to locate the exact position in the Implementation Netlist and replace the original logic with the new logic from the Reference Netlist.

Figure 6: Single error, red spot is the failing logic

For example, the following Verilog pseudo-code showcases a situation where an if-condition in a large state machine is altered by adding a new combinational signal:

always @(*) begin

case(current_state[7:0])

IDLE: begin

if(comb_sig0) next_state = START;

else next_state = IDLE;

end

START: begin

if(comb_sig1&comb_sig2|!comb_sig3) next_state = STATE1;

else if(comb_sig4&comb_sig5&!comb_sig6|eco_comb_sig) next_state = STATE2;

else if(comb_sig7|comb_sig8&!comb_sig9) next_state = STATE3;

...

end

assign eco_comb_sig = pcie_mode && beacon_status; // New combinational signal

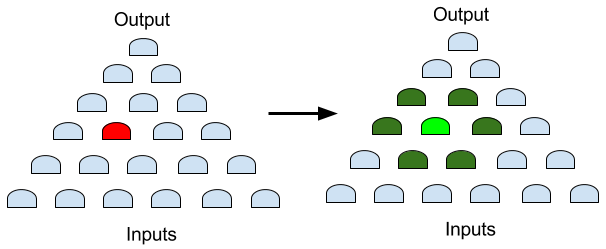

It is highly probable that Conformal ECO is unable to accurately locate the exact location to fix the combination signal change, or it may find the location but use an excessive number of gates to fix the logic, thereby affecting the surrounding logic unnecessarily. This issue with Conformal ECO occurs in at least three out of the 50 cases.

Figure 7: Conformal ECO result, dark green spots are the redundant fixes

In stark contrast, GOF ECO excels in accurately identifying the precise ECO location and generating an optimal ECO patch. GOF ECO's advanced algorithms enable it to pinpoint the exact location of the required fix with exceptional precision, ensuring that the resulting ECO patch is both minimal and efficient. This accuracy significantly reduces the impact on surrounding logic, as demonstrated in Figure 8, where only the necessary red spot is fixed, highlighting GOF ECO's efficiency and precision.

Figure 8: GOF result, only the red spot is fixed

An ECO is considered unfriendly to DFT if it impairs DFT functionality or diminishes DFT coverage. On the other hand, a DFT friendly ECO must ensure that DFT functionality remains unaffected, scan chain is intact, and clock and reset signals are manageable.

During functional ECO, the DFT logic should be set to inactive mode to prevent any functional changes from affecting it. However, in some cases, ECOs involving DFT paths may unintentionally impact the DFT logic.

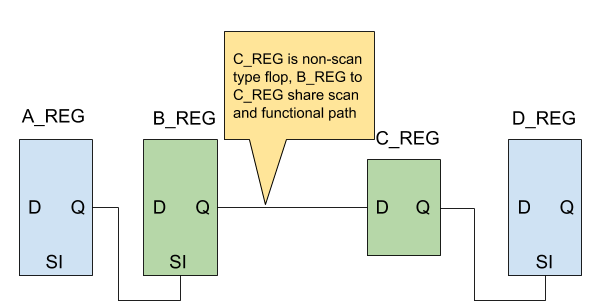

One example of this is when ECO insertion is performed on back-to-back flops in a partial scan chain, such as the one shown from A_REG to D_REG, with B_REG and C_REG forming a back-to-back path. In this scenario, it's acceptable for C_REG to be a non-scan flop prior ECO and DFT is good.

Figure 9: Scan Chain with back-to-back flops

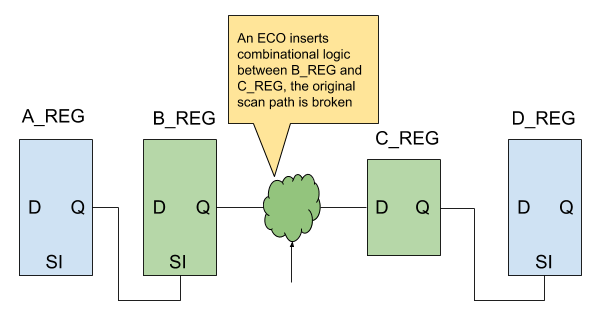

If an ECO inserts combinational logic between B_REG and C_REG in a scan chain that goes from A_REG to D_REG, and C_REG is a non-scan flop, then the scan chain is broken, as shown in Figure 10. Conformal ECO breaks DFT by directly inserting logic in the back-to-back path in this type of ECO, without considering the need to keep the scan chain.

Figure 10: ECO inserts logic into back-to-back path

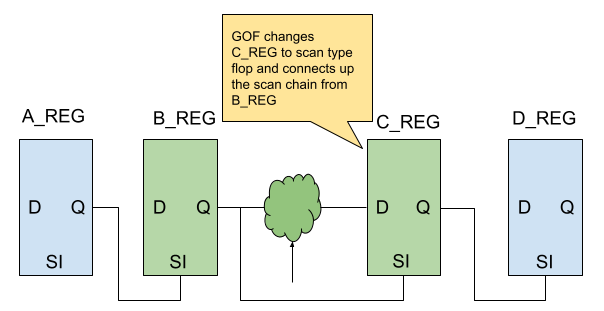

To address the scan chain breakage caused by the ECO, GOF's solution involves changing the type of C_REG from a non-scan flop to a scan flop, and connecting the scan chain properly as depicted in Figure 11.

Figure 11: GOF fixes the DFT logic by reconnecting up the Scan Chain

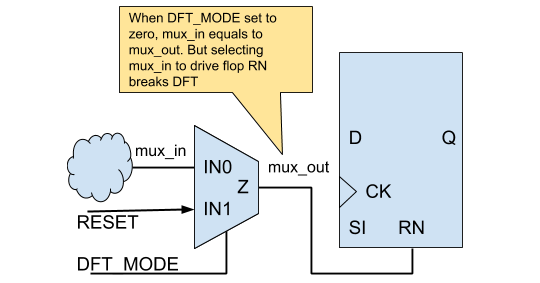

To ensure DFT logic remains inactive during functional ECO, the DFT_MODE signal is set to zero. However, some nets may be equivalent but not suitable for DFT, which can lead to DFT being broken. For instance, in Figure 12, an ECO must select either the mux_in or mux_out signal to drive a reset pin of a flop. Although the two signals are equivalent, Conformal ECO selects mux_in, which breaks DFT. In contrast, GOF can identify the MUX and chooses mux_out as the correct signal for the reset pin, thus maintaining the integrity of DFT logic.

Figure 12: Pick the right signal to maintain DFT logic

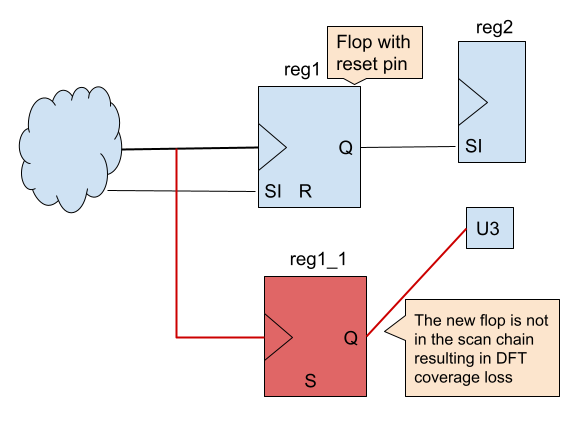

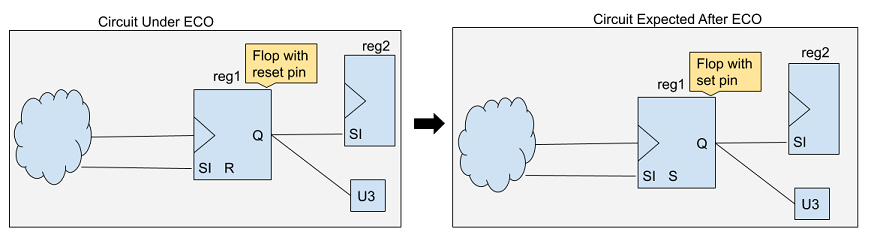

When performing functional netlist ECO, it is common to swap between resettable and settable flop types. This operation is assumed to be a simple and straightforward swapping of the same flop instance. However, in figure 13, Cadence Conformal introduces a redundant approach by using a new settable type flop reg1_1 instead of directly converting the original flop to a settable type. The new flip-flop reg1_1 drives the original functional circuit, while the old flip-flop reg1 drives the scan chain fanout reg2. This approach presents two major issues. Firstly, the new flip-flop reg1_1 is not included in the scan chain. In situations where there are many such reset/set flop swaps (around 0.2% of all flop count), there will be an approximately 0.2% loss in ATPG at-speed coverage. Secondly, Conformal LEC fails to consider the new flip-flop reg1_1 as an equal key point of reg1, resulting in numerous non-equivalent points in the equivalence report after the ECO.

Figure 13: Cadence Conformal causes DFT coverage loss in resettable/settable flop swapping ECO

While, in the ECO shown in Figure 14, GOF utilizes a direct approach of changing the flip-flop type from resettable to settable, resulting in the preservation of the scan chain and ensuring that DFT coverage remains unaffected.

Figure 14: Resettable flop swapped to settable type in ECO

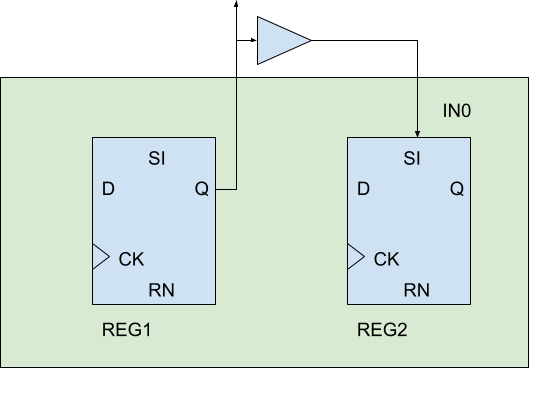

One error is common in Cadence Conformal ECO, "Error: Duplicate fanout branch # for net 'IN#'"

The issue typically arises in a scenario where a flip-flop (REG1) has its Q output connected to the parent level, and the same output is also connected to the scan input (SI) pin of another flip-flop (REG2). When an ECO is performed on REG1, such as changing its type to a set-type flip-flop, this can cause an error to occur in Conformal ECO, potentially leading to the tool stopping its operation.

Figure 15: Cadence Conformal errors out in boundary wire changes

Based on the comparison between Conformal and GOF for ECO cases, it appears that GOF is a more efficient and reliable tool for ECO implementation. The issues with Conformal, such as poor performance in dealing with certain ECOs and bugs that affect its stability and performance, suggest that GOF is a better option for designers looking to achieve smaller patch sizes and more stable ECO runs. Overall, GOF is the more effective tool for implementing ECOs when compared to Conformal.