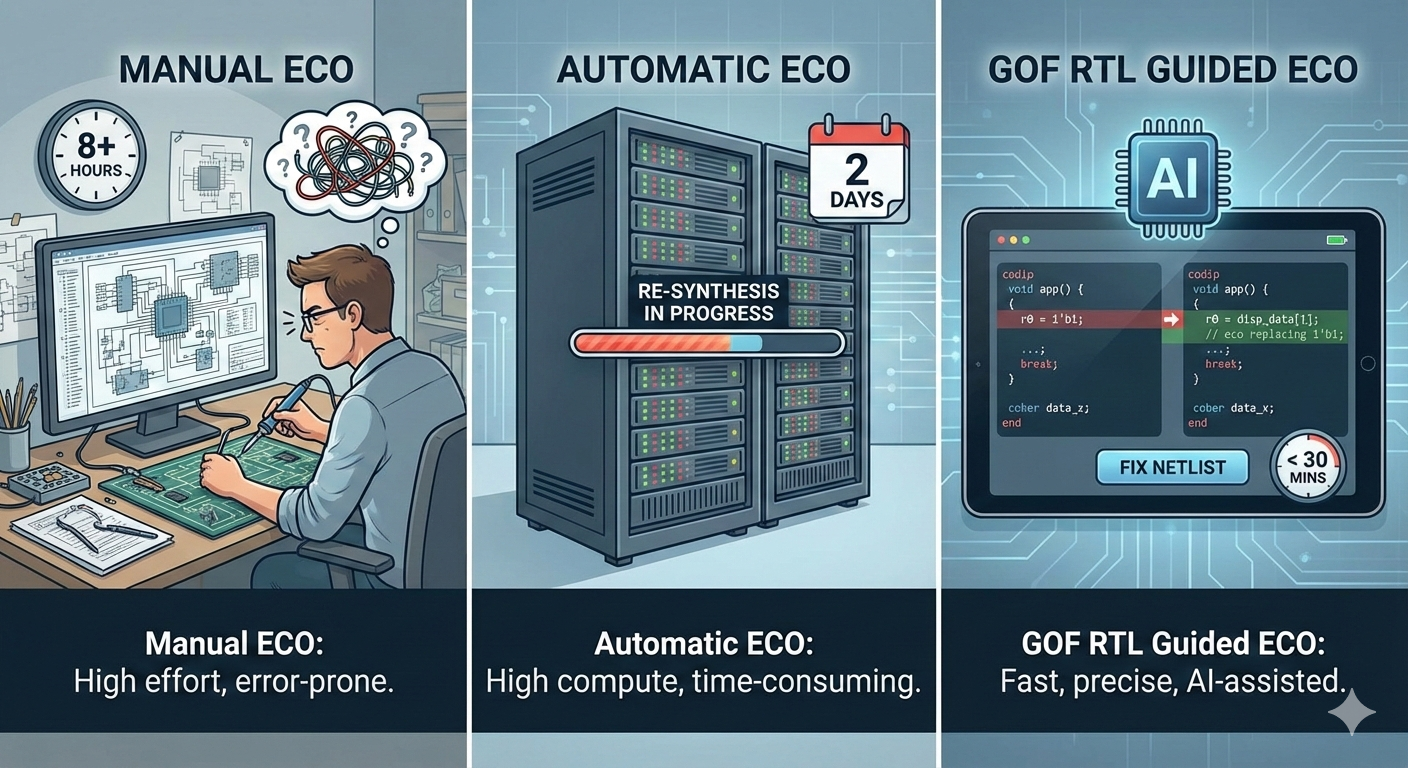

Managing a functional Engineering Change Order (ECO) in a high-density design is a high-stakes balancing act. In this scenario, we are dealing with a 2 million gate design where a single signal needs to be re-routed.

The change is deceptively simple: instead of tying r0 to a constant high value, it now needs to track bit [1] of the disp_data bus during a specific case.

2'b01: begin

if (disp_data[17:13] == 5'h1f)

- r0 = 1'b1;

+ r0 = disp_data[1]; // eco replacing 1'b1;

else

r0 = 1'b0;

Using a schematic tool to find the exact gate driving r0 inside a 2-million gate netlist is like looking for a needle in a haystack—while the haystack is on fire.

Most EDA tools require a full re-synthesis to understand the RTL change before they can attempt to patch the netlist.

GOF utilizes the RTL diff shown above to perform a surgical strike. It identifies the exact gates that need to be swapped and completes the task in under 30 minutes.

By providing the tool with both the original and modified RTL, GOF automates the comparison and the netlist fix:

read_library("../lib/tsmc3nm.lib");

read_rtl('-ref', 'modified_rtl.sv');

read_rtl('-imp', 'original_rtl.sv');

set_top('the_chip_top');

rtl_compare;

read_design("-imp", "netlist_under_eco.v");

set_top("the_chip_top");

fix_design();For those who prefer a conversational interface, GOF AI makes it even simpler:

gofai do rtl guided eco original rtl original_rtl.sv modified rtl modified_rtl.sv netlist netlist_under_eco.v top module the_chip_topThe result? A verified, gate-level patch delivered before your second cup of coffee is cold.